# The Training Stand Controlled Remotely for ADC Study

# L. Michaeli, M. Godla, J. Šaliga, J. Liptak

## Deptartment of Electronics and Multimedia Communications, FEI TU of Košice, Slovak Republic, Email: linus.michaeli@tuke.sk

Abstract. The training stand (measuring workplace) controlled remotely allows students performing laboratory exercises in the course "Microelectronics" by the analog to digital converters (ADCs) with adjustable error characteristics using standardized testing procedures. Each training workplace is accessible independently across the Internet. The control program for all training workplaces was developed in the LabVIEW. Remote user can change stimulating signals, character of ADC error function represented by integral nonlinearity and noise through html protocol using any web browser with installed plug-in Run-time engine by NI. Front panel of the workplace simulates real laboratory instruments. The training stand for simulation of ADC properties and the testing by standardized methods is a part of the virtual laboratory where other measuring stands controlled remotely are being built.

Keywords: Remote Teaching Laboratory, ADC Test and Simulation, LabVIEW

## 1. Introduction

Explanation of ADC testing methods requires prevalence of the practical exercises for better understanding of the testing procedures. Laboratory stands for ADC testing have to be equipped by the expensive precise instruments and laboratory task is rather time consuming. This limits the applicability of laboratory exercises focused on single testing procedure. The virtual laboratory stands simulating ADC converters with the error parameters involved by the user and possibility to measure them by the chosen testing procedure are the tools reducing these drawbacks of real testing laboratory for education. Remote control of those stands allows students to perform practical exercises through internet. Proposed stand represents new components in the continuously built virtual laboratory at the department of authors (html://meas-lab.fei.tuke.sk) [3].

The paper presents four testing workplaces with simulated AD converter where the integral nonlinearity is designed by the user. The nonlinearity could be proposed in various forms. First one is represented by the continuous polynomial function which is typical for ADCs with inherent integration principle. Here the order of polynomial function is two and user can select maxmal value of INL. The second possibility is integral nonlinearity in the form the sum of N characteristic DNLj values joint with each code bit position according the rules described in [1]. Periodicity and initial code shift depends on the implemented architecture. The properties corresponding to the Rademacher functions are typical for SAR ADCs while the harmonic periodicity for highest two code bits is typical for cyclic ADCs. The user can select characteristic DNLj values. Third possibility is random occurrence of DNL(k), typical for flash ADCs, with the maximal value selected by user. The last possibility is linear selectable nonlinear function with selectable offset and gain coefficients.

## 2. Design of Workplaces for the Training of ADC Tests

The proposed system consists of following testing stands:

- 1. The stand for assessment of the standardized static test.

- 2. The stand for dynamic testing methods by i) FFT test, ii)histogram test and iii) best fitting method

- 3. The laboratory stand controlled remotely for FFT test provided on the real ADC.

The acquired data for each testing stand for simulated error function as input block for an ideal ADC converting block allow to calculate functional ADC characteristics *INL*, *DNL* and integral error features like THD, SINAD, ENOB. These parameters are computed according to the IEEE standard test method for Analog to Digital converter [2].

The measurement of transient code levels T[k] for one selected code k allows students to understand the testing principle in the reduced time. The student has to chose two voltages  $V_{\rm H}(k)$ ,  $V_{\rm L}(k)$  around expected transient code level T[k]. The code level T[k] is estimated by them using information about code bin width Q from the panel and chosen code value k. For the selected record length program determines the probabilities  $P(k \le k_{test}/V_L) = P_{\rm L}$ ,  $P(k \le k_{test}/V_H) = P_{\rm H}$  and for voltages  $V_{\rm H}$ ,  $V_{\rm L}$  respectively. The user has to select both voltages until the probabilities are slightly around 50%, one lover and other higher. The measured transition code level T[k] is calculated of-line by the equation (1)

$$T[k_{test}] = \frac{0.5}{(P_H V_L - P_L V_H)} \frac{(V_H - V_L)}{(P_H - P_L)}$$

(1)

On the base of the measured T[k] levels the user can of-line calculate ADC nonlinearities.

$$INL[k] = \frac{T[k] - T_{id}[k]}{Q} \implies DNL[k] = \frac{T[k] - T[k-1] - Q}{Q}$$

(2)

The ideal code levels  $T_{id}[k]$  in (2) is taken from the front panel.

Testing panels for the dynamic tests use the same ADC error characteristic for all methods. It allows user to compare sensitivity of each method on chosen error parameters. The stimulus signal is harmonic function with the amplitude covering full scale range (FSR).

The dynamic method suitable for assessment of the functional parameters is the histogram test. According to standard [2] the values of the minimal and maximal occurrences are  $M_{min}$ ,  $M_{max}$ . Using the total amount of samples M the estimate of the amplitude <sup>e</sup>A and offset <sup>e</sup>C are calculated. Form the cumulative histogram  $H_c[k]$  the measured code levels <sup>e</sup>T[k] are obtained using formulae

$${}^{e}T[k] = {}^{e}C - {}^{e}A\cos\left(\pi \frac{H_{c}[k-1]}{M}\right)$$

(3)

where estimated signal parameters <sup>e</sup>A and <sup>e</sup>C are calculated according to

$$e_{C} = \frac{e_{T}\left[2^{N}-1\right]\cos\pi\frac{M_{\min}}{M}-e_{T}\left[1\right]\cos\pi\frac{M_{\max}}{M}}{\cos\pi\frac{M_{\min}}{M}+\cos\pi\frac{M_{\max}}{M}} \quad , e_{A} = \frac{e_{T}\left[2^{N}-1\right]-e_{T}\left[1\right]}{\cos\pi\frac{M_{\min}}{M}+\cos\pi\frac{M_{\max}}{M}} \quad (4)$$

Nonlinearities of simulated ADC are calculated by the equation (2). Taken into account terminal definition DNL must be corrected by the mean value  $DNL_{Cor}[k] = DNL[k] - (\sum_{i=1}^{N-1} DNL[i])$

ADC parameters THD, SNR and SINAD will be computed in the case of the FFT dynamic test. User has possibility to asses also impact of the incoherency between testing signal and

recording period. Another utility is the selection of the window functions. Final value of total harmonic distortion is calculated from the FFT spectra by

$$THD = \sqrt{\sum_{h=2}^{m} X_{rms}^2(f_h)} / X_{rms}(f_1)$$

(5)

where  $X_{\text{rms}}(f)$  is effective value of harmonic frequency *f*. Next parameter which user can obtain from the program is *SINAD*<sub>dB</sub>.

$$SINAD_{dB} = 20 \log \frac{A_{1rms}}{eff.value\_of\_noise}$$

(6)

Here,  $A_{1rms}$  is amplitude of stimulated sine signal in the spectrum. The calculated value of  $SINAD_{dB}$  from equation (6) allows estimate even the effective number of bits ENOB.

$$ENOB = N - \log_2 \frac{\eta_{rms}}{Q} \sqrt{12} = \frac{SINAD - 1.76}{6.02}$$

(7)

The best fitting method utilise three and four parametric estimation of the stimulus input signal. The effective value of noise RMS for ENOB  $\eta_{\rm rms}$  represents difference between best fitted function and recorder file y(m). It allows to calculate ENOB as reduction of the resolution N caused by the deterioration of the ideal quantization noise  $Q/\sqrt{12}$  by of the real noise (7).

noise (7)

$$\eta_{rms} = \sqrt{\frac{1}{M} \sum_{m=1}^{M-1} [y(m) - A\cos(2m\pi f_{in}) - B\sin(2m\pi f_{in}) - C]^2}$$

(8)

All dynamic testing panels allow users to study impact of the record length, amplitude and frequency of the stimulus signal and sampling on the measurement precision.

Workplace for the remote laboratory tests utilize the 12-bit SAR ADC (AD574A) which is controlled by the NI USB 6008 card. The stimulus signal is generated by the DAQ card NI PCI 6251 with the resolution 16 bits and sampling frequency 2,86 MS/s. Combination of both components allow to test ADC UT for various frequencies by FFT test. Identical error characteristics of simulated ADC with measured ADC allow to compare simulated and measured testing results.

#### 3. Design of Workplaces for the Training of ADC Tests

Application software was developed in the LabVIEW. LabVIEW built in web server is used for publishing on the Internet. The server publishes front panels of applications in the form of web pages and performs interactions among remote users and applications control. Any web browser with installed plug-in Run-time engine by National Instruments is available for remote control by user. Distant clients are managed by the LabVIEW web server that ensures also transferring of the access among clients according the administrator's rules. Dynamic sharing hardware in laboratory stand is internally controlled by semaphores.

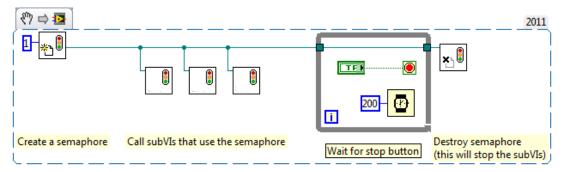

Fig. 1. Program for control of whole work stand.

The semaphore (Fig.1.) is the way how to create a group of tasks virtually running in parallel on the same hardware. The virtual parallel running is based on the fact that human sensing is much slower that a measured process similarly as it is in movie or TV. Every application is running only necessary time for test DUT and the data processing. This solution gives more effective exploitation of the measuring hardware in the laboratory stands.

Access to the described Laboratory Workplace is permanently open. The system allows monitoring activities of students enrolled in the course. Results of monitoring and answer on short questioner give possibility teacher to evaluate students attending virtual laboratory and gives new suggestions to improve testing stand. Whole idea about learning through the internet offers students first touch with electronics and instruments. Afterwards students will be able to deal with real laboratory equipment and circuits especially.

#### 4. Conclusions

Presented testing stands give students possibility to become familiar with AD converters and standardized testing methods. An ADC is available for performing basic ADC tests on real ADC component and role of all control signals. Measurements are executed in subject Basic of Electronics in a testing mode. Testing stand with simulated ADC is still in process of improving.

## Acknowledgements

The work is a part of project supported by the Educational Grant Agency of Slovak republic (No. 029TUKE-4/2012).

## References

- [1] Arpaia P, Daponte P, Michaeli L. The influence of the architecture on ADC modelling, *IEEE Trans. on Instrumentation and Measurement*, Vol. 48, No. 5, October 1999, 956-967.

- [2] IEEE Std. 1241 2010, "IEEE Standard for Terminology and Test Methods for Analogto-Digital Converters", Institute of Electrical and Electronics Engineers, Inc. New York, USA Rev. 2010.

- [3] Godla M, Michaeli L, Šaliga J, Sekerák M. The Measuring Workplace for Studying Basic Characteristic of Operational Amplifiers with Remote Access Across the Internet : Measurement 2011 : 8th International Conference on Measurement, Smolenice, Slovakia.

Bratislava : Veda, 2011. - ISBN 978-80-969-672-4-7, 274-277.

- [4] Vargha B, Shoukens J, Rolain Y. Non-linear Model Based Calibration of A/D Converters, Proc. of the 6th EWADC, Lisbon, Portugal, Sept.2001, 79-83.

[5] Arpaia P, Daponte P, Rapuano S. A state of the art on ADC modelling. *Comp. Stand.* & *Interf.*, vol.26, No.1. January 2004, 31-42.